Tenstorrent Announces RISCV Core Verification Kit

Find the Tenstorrent RISCV Core Verification Kit here.

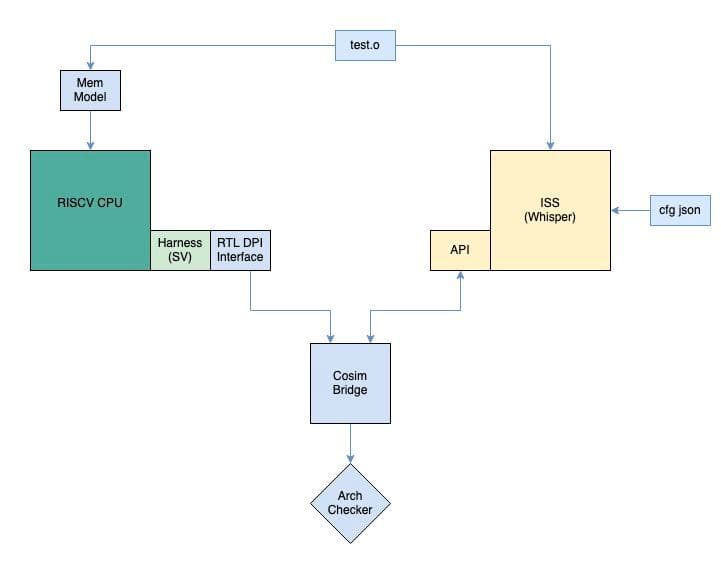

Tenstorrent is excited to announce a foundational component for the architectural verification of any RISCV based design. It works in conjunction with Whisper, a high performance open source instruction set simulator (ISS) which has been significantly enhanced by the Tenstorrent team. The core verification kit provides any RISCV based design the ability to do a step by step comparison of the RTL with the ISS.

DV is a significant challenge for CPUs and this RISCV core DV Kit provides a seamless way to capture interesting architectural state. It extracts the content of the DUT via a harness and provides hooks into the ISS to run the simulation in lock step thus providing early visibility into design divergence. In addition to arch state, other capabilities that can be extracted include workload traces, architectural performance events, table walks, CSRs, etc. This cosim flow is designed to be compatible with Emulation/FPGA platforms.

We will continue to release additional components critical for the architectural verification of a RISCV based CPU such as – a Memory Consistency model/checker, an Architectural test suite and Architectural coverage source code to measure the efficacy of stimulus. We encourage the open source community to use these and provide feedback. Open access to infrastructure components such as these is critical for the expansion of the RISCV ecosystem.