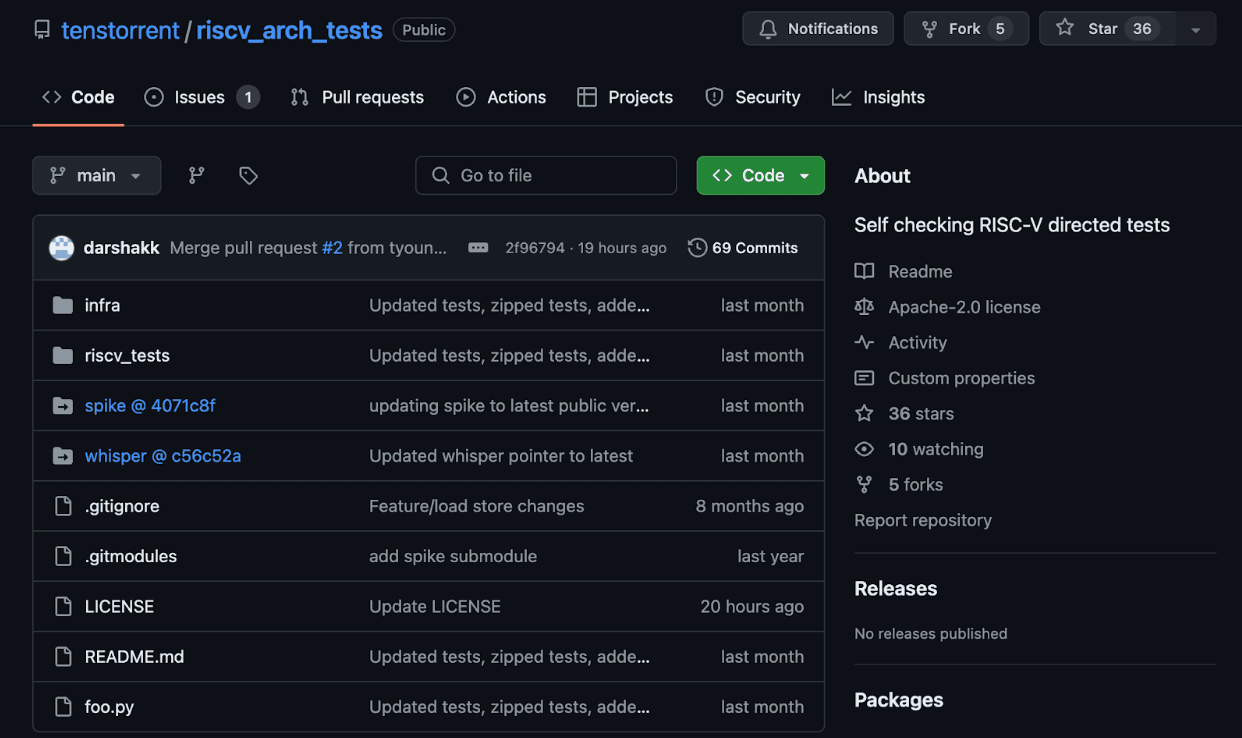

Tenstorrent is Continuing its Contributions to the RISC-V Open Source Ecosystem

GitHub found here. This is arguably the most comprehensive open-source RISC-V compatibility suite with over 13,000 tests that cover a broad spectrum of RISC-V ISA:

- RV64-I

- RV-M

- RV-F

- RV-D

- RV-C

- RV-V

- Zfh

- Zba, Zbb, Zbc, Zbs

In addition to the elf files, we are also including the disassembly for all tests for ease of debug and visualization. These tests are meant to be agnostic to the underlying microarchitectural implementation and can be simulated on widely adopted RISC-V instruction set simulators by the Open Source community (whisper, spike). The tests are generated via internal tools but use the ISA spec from riscv-opcodes, maintained by RVI.

We will continue to add to these tests and support additional ISA extensions on RISC-V as they are introduced, starting with support for the full RVA23 profile. In addition, we are also supporting and upgrading the Tenstorrent release for whisper. This includes not only newer ISA extensions but also additional software models needed to deploy Whisper in a real world functional simulation environment with IO and memory devices.

Tenstorrent's RISC-V tools can be deployed individually or together to provide a comprehensive functional environment for any CPU design-under-test; they include a Reference Model, Architectural Compat Suite, Integration Testbench. These tools can also be leveraged in an Emulation environment. Tenstorrent uses them internally to qualify our high performance designs and we will continue to improve them.

All tests are now live in Tenstorrent’s GitHub repository – we are also open to supporting broadly applicable changes to the tests and absolutely welcome requests for any fixes!